# EDU1000 Datasheet CMOS MOSFET ARRAY

(Acknowledgement: Special thanks to Texas Instruments for their generous support for providing these MOS array chips)

# **RECOMMENDED OPERATING CONDITIONS:**

Nominal operating conditions should be selected so that the operation is always within the following ranges:

| CHARACTERISTIC / PARAMETER | TYPICAL  | UNITS               |

|----------------------------|----------|---------------------|

| Vin                        | 0 to 2.5 | V                   |

| Vdd,max                    | 3        | V                   |

| μCox                       | 150      | μA / V <sup>2</sup> |

| Vtn                        | 0.5      | V                   |

| λ                          | .015     | $V^{-1}$            |

| Y                          | 0.6      | V <sup>0.5</sup>    |

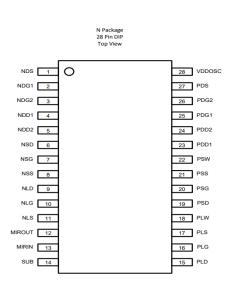

### **PIN CONFIGURATION:**

### **PIN FUNCTIONS:**

| Pin |        | Description                          |  |

|-----|--------|--------------------------------------|--|

| No. | Name   |                                      |  |

| 1   | NDS    | NMOS Differential Pair Shared Source |  |

| 2   | NDG1   | NMOS Differential Pair Gate 1        |  |

| 3   | NDG2   | NMOS Differential Pair Gate 2        |  |

| 4   | NDD1   | NMOS Differential Pair Drain 1       |  |

| 5   | NDD2   | NMOS Differential Pair Drain 2       |  |

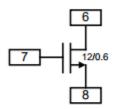

| 6   | NSD    | NMOS Short Channel Drain             |  |

| 7   | NSG    | NMOS Short Channel Gate              |  |

| 8   | NSS    | NMOS Short Channel Source            |  |

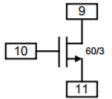

| 9   | NLD    | NMOS Long Channel Drain              |  |

| 10  | NLG    | NMOS Long Channel Gate               |  |

| 11  | NLS    | NMOS Long Channel Source             |  |

| 12  | MIROUT | NMOS Mirror Output (Drain)           |  |

| 13  | MIRIN  | NMOS Mirror In (Gate + Drain)        |  |

| 14  | SUB    | Chip Substrate (P type)              |  |

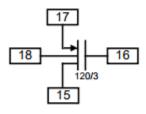

| 15  | PLD    | PMOS Long Channel Drain              |  |

| 16  | PLG    | PMOS Long Channel Gate               |  |

| 17  | PLS    | PMOS Long Channel Source             |  |

| 18  | PLW    | PMOS Long Channel Well (Bulk)        |  |

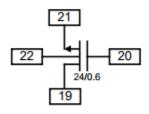

| 19  | PSD    | PMOS Short Channel Drain             |  |

| 20  | PSG    | PMOS Short Channel Gate              |  |

| 21  | PSS    | PMOS Short Channel Source            |  |

| 22  | PSW    | PMOS Short Channel Well (Bulk)       |  |

| 23  | PDD1   | PMOS Differential Pair Drain 1       |  |

| 24  | PDD2   | PMOS Differential Pair Drain 2       |  |

| 25  | PDG1   | PMOS Differential Pair Gate 1        |  |

| 26  | PDG2   | PMOS Differential Pair Gate 2        |  |

| 27  | PDS    | PMOS Differential Pair Shared Source |  |

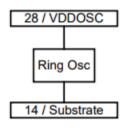

| 28  | VDDOSC | Positive Supply for Ring Oscillator  |  |

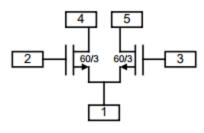

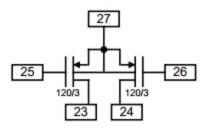

# MOS CONFIGURATIONS: W/L values indicated

#### **Differential Pairs**

Short Channel Transistors

Long Channel Transistors

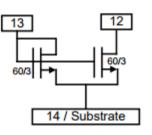

Current Mirror

**Ring Oscillator**

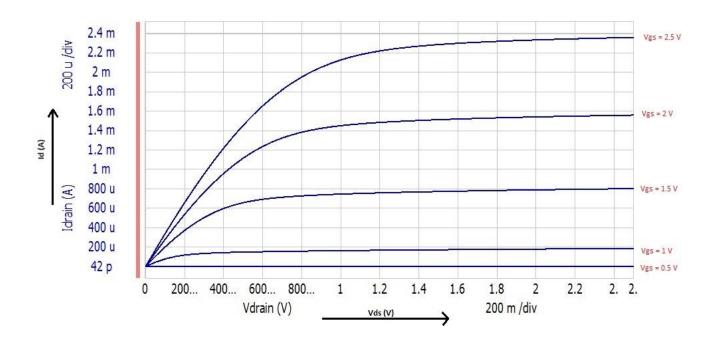

# I-V CHARACTERISTICS:

#### 2.7 m Vgs = 2.5 V 200 u /div 2.4 m 2.2 m 2 m 1.8 m (A) b1 1.6 m Vgs = 2 V 1.4 m 1.2 m 1 m Idrain (A) 800 u 600 u Vgs = 1.5 V 400 u 200 u Vgs = 1 V 17 p Vgs = 0.5 V 0 200 m 400 m 600 m 800 m 1 1.2 1.4 1.6 1.8 2 2.2 2.4 2.5 200 m /div Vdrain (V) Vds (V)

# NMOS Long Channel:

NMOS Short Channel: